# Contents

| Page | Section   | Title                                              |

|------|-----------|----------------------------------------------------|

| 5    | 1.        | Introduction                                       |

| 6    | 1.1.      | Features                                           |

| 6    | 1.2.      | Features of the MAS 35x9F Family                   |

| 7    | 1.3.      | Application Overview                               |

| 8    | 2.        | Functional Description                             |

| 8    | 2.1.      | Overview •                                         |

| 8    | 2.2.      | Architecture of the MAS 35x9F                      |

| 8    | 2.3.      | DSP Core                                           |

| 9    | 2.3.1.    | RAM and Registers                                  |

| 9    | 2.3.2.    | Firmware and Software                              |

| 9    | 2.3.2.1.  | Internal Program ROM and Firmware, MPEG-Decoding   |

| 9    | 2.3.2.2.  | Program Download Feature                           |

| 10   | 2.4.      | Audio Codec                                        |

| 10   | 2.4.1.    | A/D Converter and Microphone Amplifier             |

| 10   | 2.4.2.    | Baseband Processing                                |

| 10   | 2.4.2.1.  | Bass, Treble, and Loudness                         |

| 10   | 2.4.2.2.  | Micronas Bass (MB)                                 |

| 10   | 2.4.2.3.  | Automatic Volume Control (AVC)                     |

| 10   | 2.4.2.4.  | Balance and Volume                                 |

| 11   | 2.4.3.    | D/A Converters                                     |

| 11   | 2.4.4.    | Output Amplifiers                                  |

| 11   | 2.5.      | Clock Management                                   |

| 11   | 2.5.1.    | DSP Clock                                          |

| 11   | 2.5.2.    | Clock Output At CLKO                               |

| 12   | 2.6.      | Power Supply Concept                               |

| 12   | 2.6.1.    | Power Supply Regions                               |

| 12   | 2.6.2.    | DC/DC Converters                                   |

| 13   | 2.6.3.    | Power Supply Configurations                        |

| 15   | 2.7.      | MP3 Block Input Mode                               |

| 15   | 2.7.1.    | Functional Description of the MP3 Block Input Mode |

| 16   | 2.7.2.    | Setup                                              |

| 16   | 2.7.2.1.  | Resync Timeout                                     |

| 16   | 2.7.2.2.  | Detailed Setup                                     |

| 16   | 2.8.      | Battery Voltage Supervision                        |

| 16   | 2.9.      | Interfaces                                         |

| 16   | 2.9.1.    | I2C Control Interface                              |

| 16   | 2.9.2.    | S/PDIF Input Interface                             |

| 16   | 2.9.3.    | S/PDIF Output                                      |

| 17   | 2.9.4.    | Multiline Serial Audio Input (SDI, SDIB)           |

| 17   | 2.9.5.    | Multiline Serial Output (SDO)                      |

| 17   | 2.9.6.    | Parallel Input/Output Interface (PIO)              |

| 17   | 2.10.     | MPEG Synchronization Output                        |

| 18   | 2.11.     | Default Operation                                  |

| 18   | 2.11.1.   | Stand-by Functions                                 |

| 18   | 2.11.2.   | Power-Up of the DC/DC Converters and Reset         |

| 19   | 2.11.2.1. | Important Advice for Turn-on and Operating Voltage |

# Contents, continued

| Page | Section   | Title                                                                               |

|------|-----------|-------------------------------------------------------------------------------------|

| 20   | 2.11.3.   | Reset Signal Specification                                                          |

| 21   | 2.11.4.   | Control of the Signal Processing                                                    |

| 21   | 2.11.5.   | Start-up of the Audio Codec                                                         |

| 21   | 2.11.6.   | Power-Down                                                                          |

|      | _         |                                                                                     |

| 22   | 3.        | Controlling                                                                         |

| 22   | 3.1.      | I <sup>2</sup> C Interface                                                          |

| 22   | 3.1.1.    | Device Address                                                                      |

| 22   | 3.1.2.    | I <sup>2</sup> C Registers and Subaddresses                                         |

| 22   | 3.1.3.    | Naming Convention                                                                   |

| 22   | 3.2.      | Direct Configuration Registers                                                      |

| 23   | 3.2.1.    | Write Direct Configuration Registers                                                |

| 23   | 3.2.2.    | Read Direct Configuration Register                                                  |

| 28   | 3.3.      | DSP Core                                                                            |

| 28   | 3.3.1.    | Access Protocol                                                                     |

| 29   | 3.3.2.    | Data Formats                                                                        |

| 29   | 3.3.2.1.  | Run and Freeze (Codes 0hex to 3hex)                                                 |

| 29   | 3.3.2.2.  | Read Register (Code A <sub>hex</sub> )                                              |

| 29   | 3.3.2.3.  | Write Register (Code B <sub>hex</sub> )                                             |

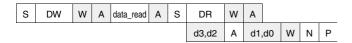

| 30   | 3.3.2.4.  | Read Memory (Codes C <sub>hex</sub> and D <sub>hex</sub> )                          |

| 30   | 3.3.2.5.  | Short Read Memory (Codes C4 <sub>hex</sub> and D4 <sub>hex</sub> )                  |

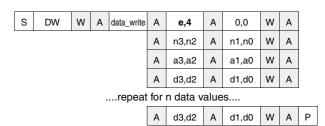

| 30   | 3.3.2.6.  | Write Memory (Codes Ehex and Fhex)                                                  |

| 30   | 3.3.2.7.  | Short Write Memory (Codes E4 <sub>hex</sub> and F4 <sub>hex</sub> )                 |

| 30   | 3.3.2.8.  | Clear SYNC Signal (Code 5hex)                                                       |

| 31   | 3.3.2.9.  | Default Read                                                                        |

| 31   | 3.3.2.10. | Fast Program Download (Code 6 <sub>hex</sub> )                                      |

| 31   | 3.3.2.11. | Serial Program Download                                                             |

| 32   | 3.3.2.12. | Read IC Version (Code 7 <sub>hex</sub> )                                            |

| 32   | 3.3.3.    | List of DSP Registers                                                               |

| 32   | 3.3.4.    | List of DSP Memory Cells                                                            |

| 33   | 3.3.4.1.  | Application Selection and Application Running                                       |

| 33   | 3.3.4.2.  | Application Specific Control                                                        |

| 43   | 3.3.5.    | Ancillary Data                                                                      |

| 43   | 3.3.6.    | Reading of the Memory Cells "Number of Bits in Ancillary Data" and "Ancillary Data" |

| 44   | 3.3.7.    | DSP Volume Control                                                                  |

| 44   | 3.3.8.    | Explanation of the G.729A Data Format                                               |

| 45   | 3.4.      | Audio Codec Access Protocol                                                         |

| 45   | 3.4.1.    | Write Codec Register                                                                |

| 45   | 3.4.2.    | Read Codec Register                                                                 |

| 46   | 3.4.3.    | Codec Registers                                                                     |

| 52   | 3.4.4.    | Basic MB Configuration                                                              |

|      |           |                                                                                     |

# Contents, continued

| Page | Section  | Title                                                                 |

|------|----------|-----------------------------------------------------------------------|

| 53   | 4.       | Specifications                                                        |

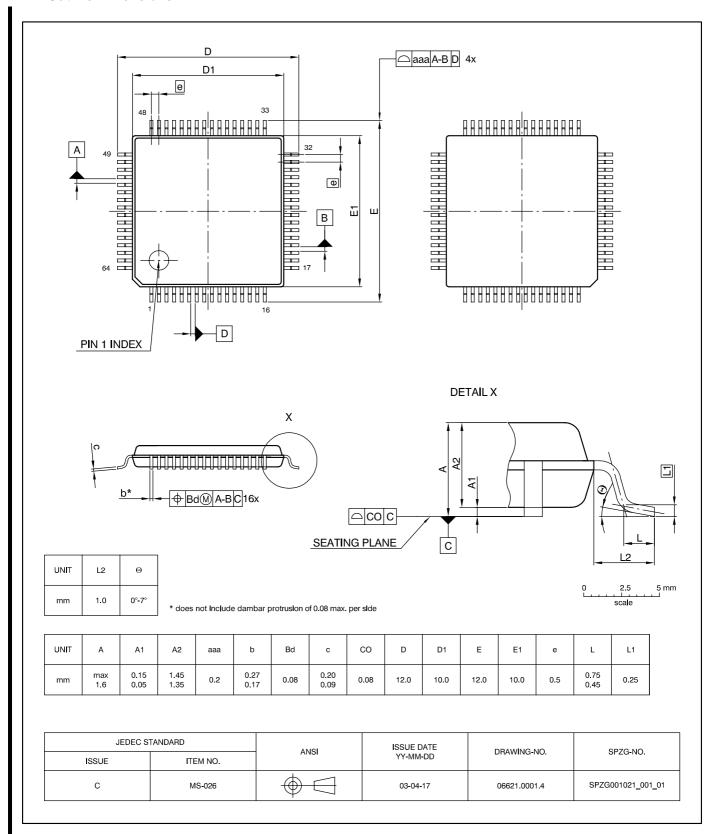

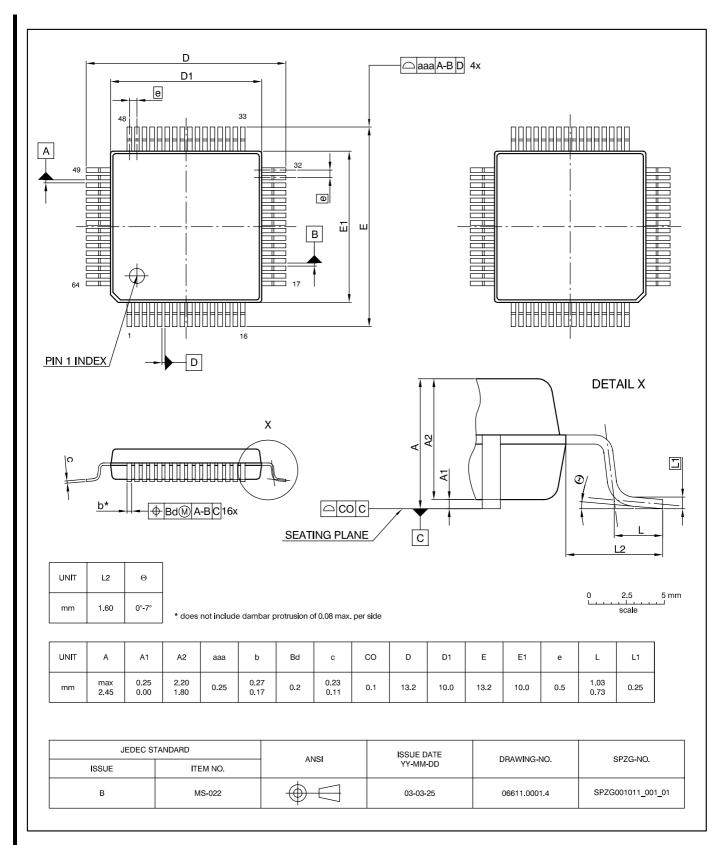

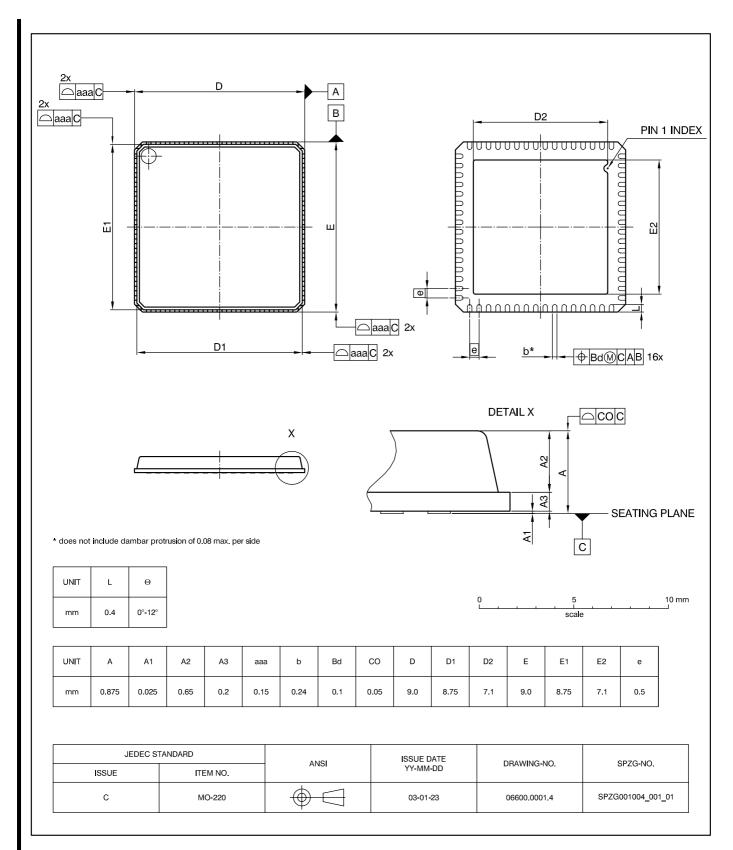

| 53   | 4.1.     | Outline Dimensions                                                    |

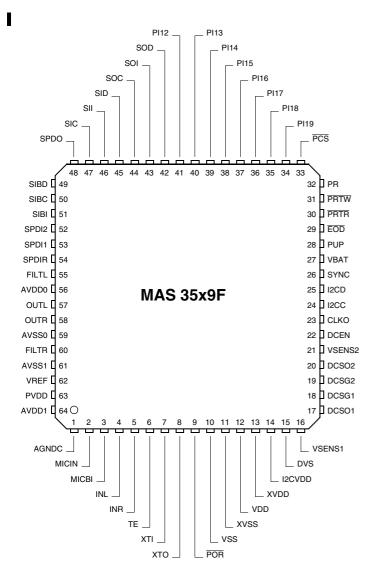

| 56   | 4.2.     | Pin Connections and Short Descriptions                                |

| 59   | 4.3.     | Pin Descriptions                                                      |

| 59   | 4.3.1.   | Power Supply Pins                                                     |

| 59   | 4.3.2.   | Analog Reference Pins                                                 |

| 59   | 4.3.3.   | DC/DC Converters and Battery Voltage Supervision                      |

| 59   | 4.3.4.   | Oscillator Pins and Clocking                                          |

| 59   | 4.3.5.   | Control Lines                                                         |

| 59   | 4.3.6.   | Parallel Interface Lines                                              |

| 60   | 4.3.6.1. | PIO Handshake Lines                                                   |

| 60   | 4.3.7.   | Serial Input Interface (SDI)                                          |

| 60   | 4.3.8.   | Serial Input Interface B (SDIB)                                       |

| 60   | 4.3.9.   | Serial Output Interface (SDO)                                         |

| 60   | 4.3.10.  | S/PDIF Input Interface                                                |

| 60   | 4.3.11.  | S/PDIF Output Interface                                               |

| 60   | 4.3.12.  | Analog Input Interfaces                                               |

| 60   | 4.3.13.  | Analog Output Interfaces                                              |

| 61   | 4.3.14.  | Miscellaneous                                                         |

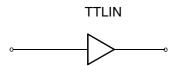

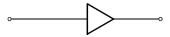

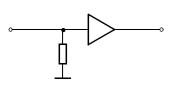

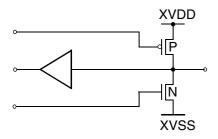

| 61   | 4.4.     | Pin Configuration                                                     |

| 62   | 4.5.     | Internal Pin Circuits                                                 |

| 63   | 4.5.1.   | Reset Pin Configuration for MAS 3529F and MAS 3539F                   |

| 64   | 4.6.     | Electrical Characteristics                                            |

| 64   | 4.6.1.   | Absolute Maximum Ratings                                              |

| 66   | 4.6.1.1. | Recommended Operating Conditions                                      |

| 69   | 4.6.2.   | Digital Characteristics                                               |

| 70   | 4.6.2.1. | I <sup>2</sup> C Characteristics                                      |

| 71   | 4.6.2.2. | Serial (I <sup>2</sup> S) Input Interface Characteristics (SDI, SDIB) |

| 72   | 4.6.2.3. | Serial Output Interface Characteristics (SDO)                         |

| 74   | 4.6.2.4. | S/PDIF Input Characteristics                                          |

| 75   | 4.6.2.5. | S/PDIF Output Characteristics                                         |

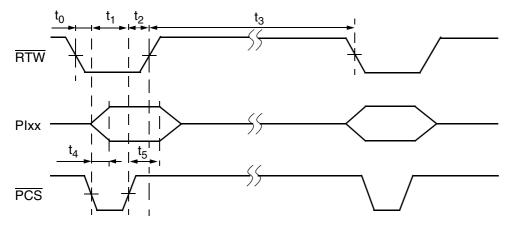

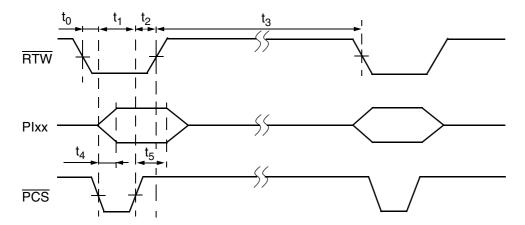

| 75   | 4.6.2.6. | PIO as Parallel Input Interface: DMA Mode                             |

| 77   | 4.6.2.7. | PIO as Parallel Input Interface: Program Download Mode                |

| 78   | 4.6.2.8. | PIO as Parallel Output Interface                                      |

| 79   | 4.6.3.   | Analog Characteristics                                                |

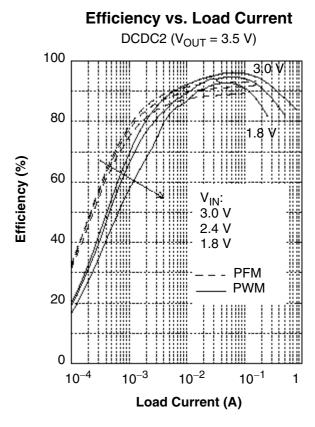

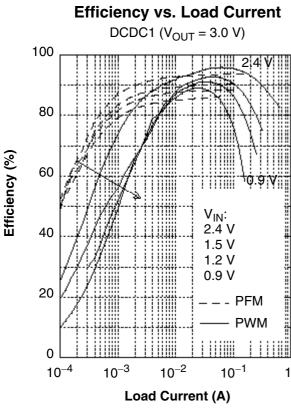

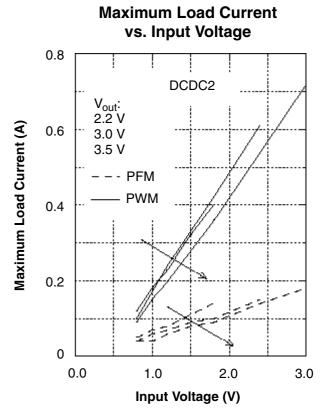

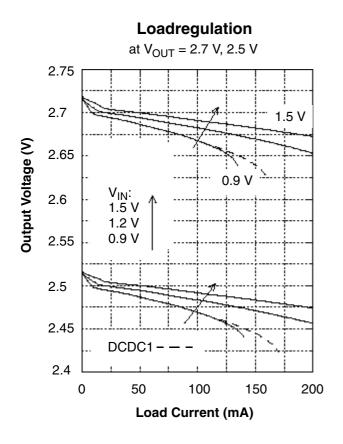

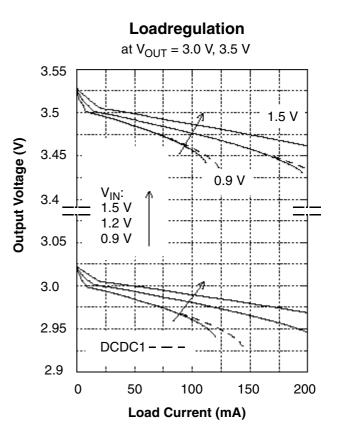

| 82   | 4.6.4.   | DC/DC Converter Characteristics                                       |

| 84   | 4.6.5.   | Typical Performance Characteristics                                   |

| 87   | 5.       | Application                                                           |

| 87   | 5.1.     | Typical Application in a Portable Player                              |

| 88   | 5.2.     | Recommended DC/DC Converter Application Circuit                       |

| 90   | 6.       | Data Sheet History                                                    |

# MPEG Layer 2/3, AAC Audio Decoder, G.729 Annex A Codec

Release Note: Revision bars indicate significant changes to the previous edition. This data sheet applies to the MAS 35x9F version B4.

#### 1. Introduction

The MAS 35x9F is a single-chip, low-power MPEG layer 2/3 and MPEG2-AAC audio stereo decoder. It also contains the G.729 Annex A speech compression and decompression technology for use in memory-based or broadcast applications. Additional functionality is achievable via download software (e.g., CELP voice decoder, Micronas SC4 (ADPCM) encoder/decoder).

The MAS 35x9F decoding block accepts compressed digital data streams as serial bit streams or in parallel format, and provides serial PCM and S/PDIF output of decompressed audio. In addition to the signal processing function, the IC incorporates a high-performance stereo D/A converter, headphone amplifiers, a stereo A/D converter, a microphone amplifier, and two DC/DC converters.

Thus, the MAS 35x9F provides a true "all-in-one" solution that is ideally suited for highly optimized memory-based portable music players with integrated speech recording and playback function.

In MPEG 1 (ISO 11172-3), three hierarchical layers of compression have been standardized. The most sophisticated and complex, layer 3, allows compression rates of approximately 12:1 for mono and stereo signals while still maintaining CD audio quality. Layer 2 (widely used, e.g., in DVD) achieves a compression of 8:1 without significant losses in audio quality.

The MAS 35x9F supports the "Advanced Audio Coding" (AAC) that is defined as a part of MPEG 2. AAC provides compression rates up to 16:1. It defines several profiles for different applications. This IC decodes the "low complexity profile" that is especially optimized for portable applications.

The MAS 35x9F also implements a voice encoder and decoder that is compliant to the ITU Standard G.729 Annex A.

SC4 is a proprietary Micronas speech codec technology that can be downloaded to the MAS 35x9F, to allow recording and playing back speech at various sampling rates.

#### 1.1. Features

#### **Firmware**

- MPEG 1/2 layer 2 and layer 3 decoder

- Extension to MPEG 2 layer 3 for low sampling rates ("MPEG 2.5")

- Extraction of MPEG Ancillary Data

- MPEG 2 AAC decoder (low-complexity profile)

- Micronas G.729 Annex A speech compression and decompression

- Master or slave clock operation

- Adaptive bit rates (bit rate switching)

- Intelligent power management (processor clock is dependent on sampling frequencies)

- SDMI-compliant security technology

- Stereo channel mixer

- Bass, treble, and loudness function

- Micronas Bass (MB)

- Automatic Volume Control (AVC)

#### Interfaces

6

- Two serial asynchronous interfaces for bit streams and uncompressed digital audio

- Parallel handshake bit stream input

- Serial audio output via I<sup>2</sup>S and related formats

- S/PDIF data input and output

- Controlling via I<sup>2</sup>C interface

#### **Hardware Features**

- Two independent embedded DC/DC converters, (e.g., for DSP and flash RAM supply)

- Low DC/DC converter start-up voltage (0.9 V)

- DC converter efficiency up to 95%

- Battery voltage monitor

- Low supply voltage down to 2.2 V

- Low power dissipation, e.g., 87 mW

(128kBit/s, 44.1 kHz, Headphone playback)

- High-performance RISC DSP core

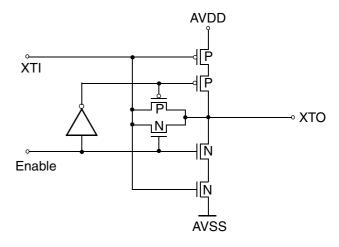

- On-chip crystal oscillator

- Hardware power management and power-off functions

- Microphone amplifier

- Stereo A/D converter for FM/AM-radio and speech input

- CD quality stereo D/A converter

- Headphone amplifier

- Noise and power-optimized volume

- External clock or crystal frequency of 13...28 MHz

- Standby current < 10 μA

#### 1.2. Features of the MAS 35x9F Family

| Feature               | 3509 | 3519 | 3529 | 3539 | 3549 | 3559 |

|-----------------------|------|------|------|------|------|------|

| Layer 3 Decoder       | Х    | Х    | Х    | X    |      |      |

| G.729 Encoder/Decoder | Х    | Х    |      |      | Х    |      |

| AAC Decoder           | Х    |      | Х    |      |      | Х    |

## 1.3. Application Overview

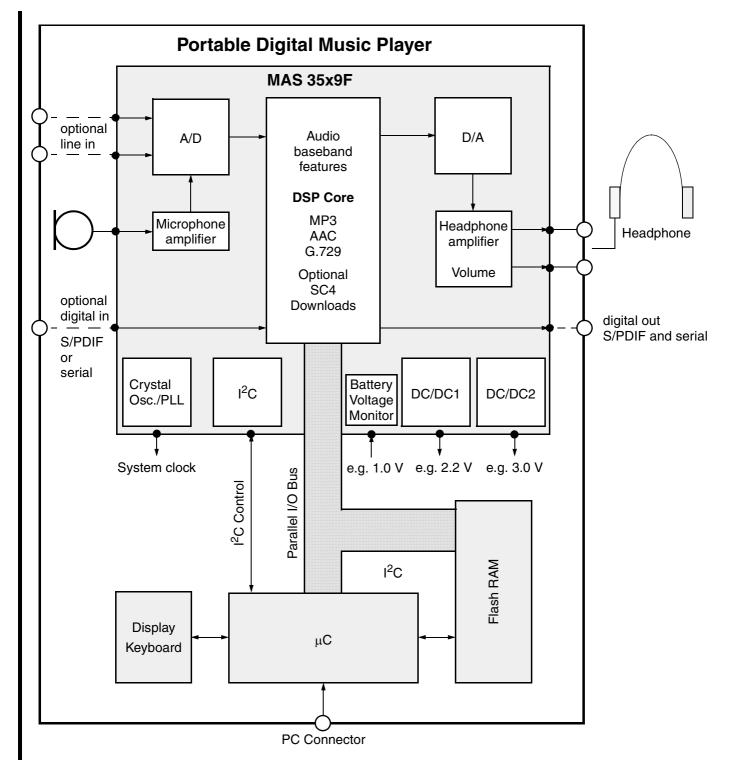

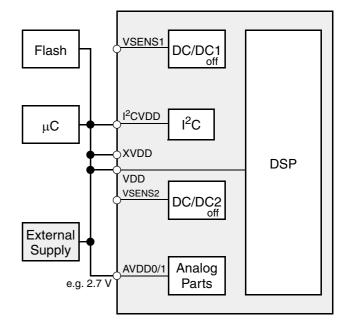

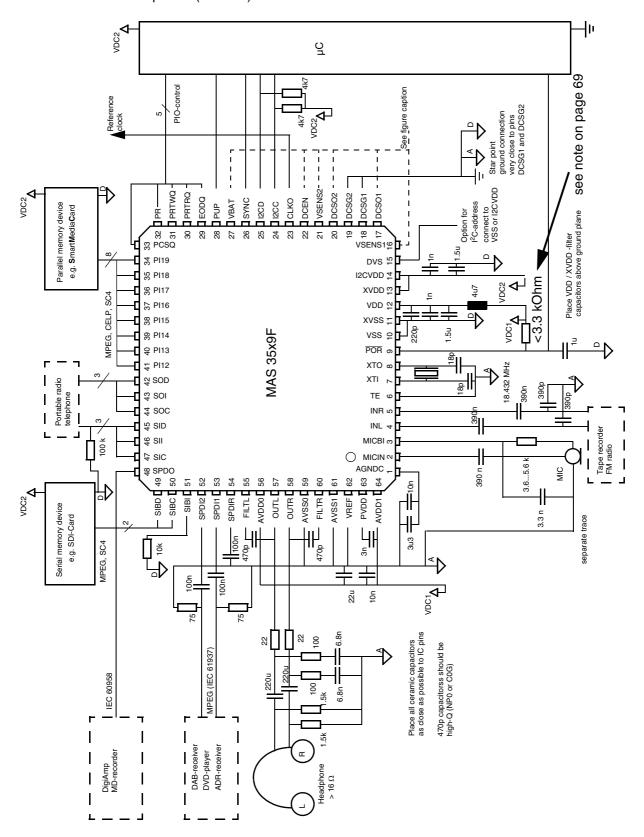

The following block diagram shows an example application for the MAS 35x9F in a portable audio player device. Besides a simple controller and the external flash memories, all required components are integrated in the MAS 35x9F. The MAS 35x9F supports both speech and radio quality audio encoding, as well as compressed-audio decoding tasks.

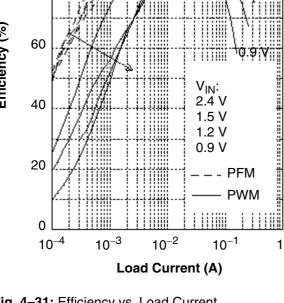

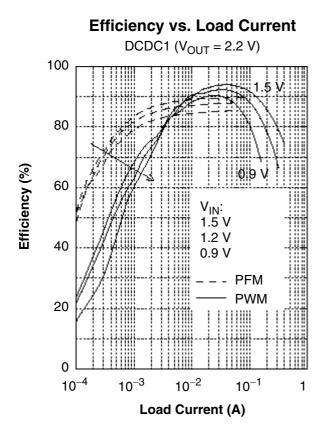

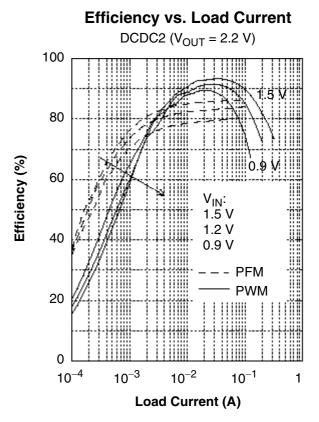

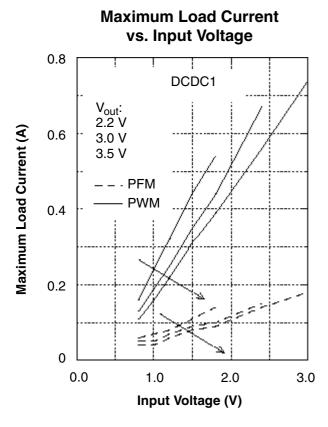

Fig. 1–1 depicts a portable power-optimized audio application. The two embedded DC/DC converters of the MAS 35x9F generate optimum power supply voltages for the DSP core and also for state-of-the art flash memories that typically require 2.7 to 3.3 V supply. The performance of the DC/DC converters reaches efficiencies of up to 95%.

Fig. 1-1: Example of an application for the MAS 35x9F in a portable audio player device

## 2. Functional Description

#### 2.1. Overview

The MAS 35x9F is intended for use in portable consumer audio applications. It receives parallel or serial data streams and decodes MPEG Layer 2 and 3 (including the low sampling frequency extensions) and MPEG 2 AAC. A low bit-rate speech codec, compliant to the ITU Standard G.729 Annex A, is integrated. Additional downloadable software modules (SDMI, other audio/speech encoders/decoders) are available on request.

#### 2.2. Architecture of the MAS 35x9F

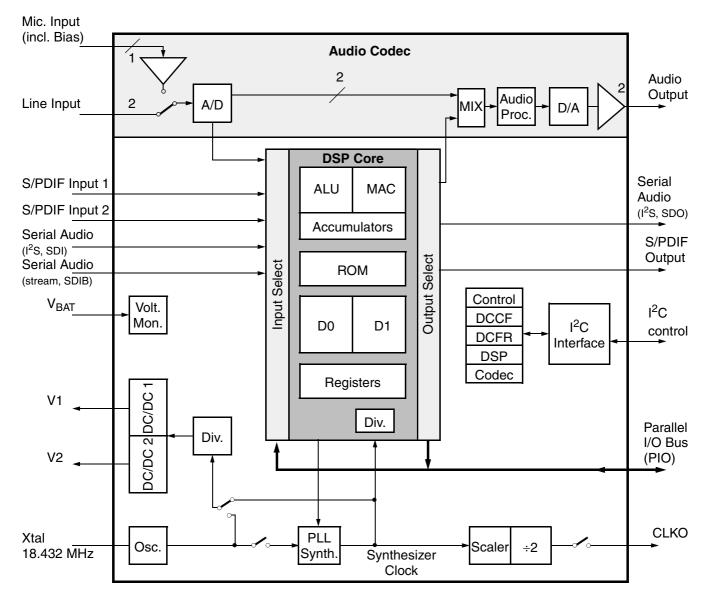

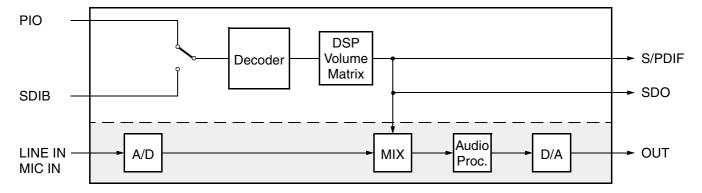

The hardware of the MAS 35x9F consists of a high-performance RISC Digital Signal Processor (DSP), and appropriate interfaces. A hardware overview of the IC is shown in Fig. 2–1.

#### 2.3. DSP Core

The internal processor is a dedicated DSP for advanced audio applications.

Fig. 2-1: The MAS 35x9F architecture

#### 2.3.1. RAM and Registers

The DSP core has access to two RAM banks denoted D0 and D1. All RAM addresses can be accessed in a 20-bit or a 16-bit mode via I<sup>2</sup>C bus. For fast access of internal DSP states the processor core has an address space of 256 data registers which also can be accessed via I<sup>2</sup>C bus. For more details, please refer to Section 3.3. on page 28.

### 2.3.2. Firmware and Software

# 2.3.2.1. Internal Program ROM and Firmware, MPEG-Decoding

The firmware implemented in the program ROM of the MAS 35x9F provides MPEG 1/2 Layer 2, MPEG 1/2/2.5 Layer 3 and MPEG 2 AAC-decoding as well as a G.729 encoder and decoder.

The DSP operating system starts the firmware in the "Application Selection Mode". By setting the appropriate bit in the Application Select memory cell (see Table 3–9 on page 33), the MPEG audio decoder or the G.729 Codec can be activated.

The MPEG decoder provides an automatic standard detection mode. If all MPEG audio decoders are

selected, the Layer 2, Layer 3 or AAC bit stream is recognized and decoded automatically.

To add/remove MPEG layers while running in MPEG decoding mode (e.g. Layer 2, Layer 3 (0x0c) to Layer 2, Layer 3, AAC (0x1c)), the application selection has to be reset before writing the new value.

For general control purposes, the operation system provides a set of I<sup>2</sup>C instructions that give access to internal DSP registers and memory areas.

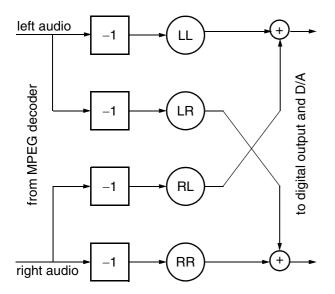

An auxiliary digital volume control and mixer matrix is applied to the digital stereo audio data. This matrix is capable of performing the balance control and a simple kind of stereo basewidth enhancement. All four factors LL, LR, RL, and RR are adjustable, please refer to Fig. 3–3 on page 44.

## 2.3.2.2. Program Download Feature

The standard functions of the MAS 35x9F can be extended or substituted by downloading up to 4 kWords (1 Word = 20 bits) of program code and additionally up to 4 kWords of coefficients into the internal RAM.

9

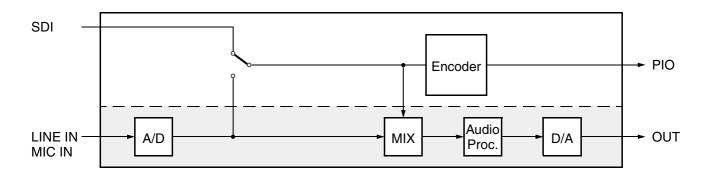

Fig. 2-2: Encoder signal flow

Fig. 2-3: Decoder signal flow

#### 2.4. Audio Codec

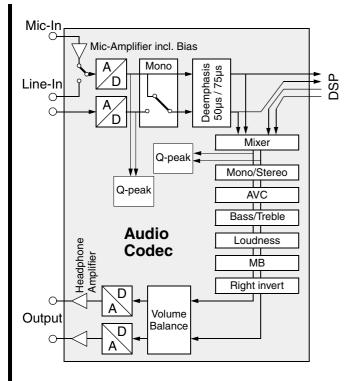

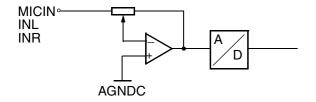

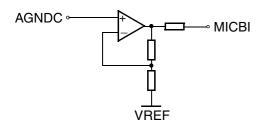

A sophisticated set of audio converters and sound features has been implemented to comply with various kinds of operating environments that range up to highend equipment (see Fig. 2–4).

Fig. 2-4: Signal flow block diagram of Audio Codec

## 2.4.1. A/D Converter and Microphone Amplifier

A pair of A/D converters is provided for recording or loop-through purposes. In addition, a microphone amplifier including voltage supply function for an electret type microphone has been integrated.

## 2.4.2. Baseband Processing

The several baseband functions are applied to the digital audio signal immediately before D/A conversion.

## 2.4.2.1. Bass, Treble, and Loudness

Standard baseband functions such as bass, treble, and loudness are provided (refer to Table 3–16 for details).

#### 2.4.2.2. Micronas Bass (MB)

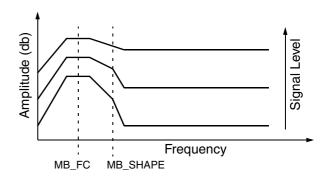

The Micronas Bass system (MB) was developed to extend the frequency range of loudspeakers or headphones below the cutoff frequency of the speakers. Apart from dynamically amplifying the low-frequency bass signals, the MB exploits the psycho-acoustic phenomenon of the 'missing fundamental'. Adding harmonics of the frequency components below the cutoff frequency gives the impression of actually hearing the low frequency fundamental, while at the same time retaining the loudness of the original signal. Due to the parametric implementation of the MB, it can be customized to create different bass effects and adapted to various loudspeaker characteristics (see Section 3.4.4. and Table 3–16).

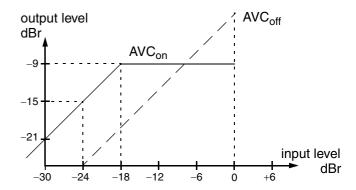

## 2.4.2.3. Automatic Volume Control (AVC)

In a collection of tracks from different sources fairly often the average volume level varies. Especially in a noisy listening environment the user must adjust the volume to comfortably enjoy listening. The Automatic Volume Correction (AVC) solves this problem by equalizing the volume level.

To prevent clipping, the AVC's gain decreases quickly in dynamic boost conditions. To suppress oscillation effects, the gain increases rather slowly for low level inputs. The decay time is programmable by means of the AVC register (see Table 3–16 on page 46).

For input levels of -18 dBr to 0 dBr, the AVC maintains a fixed output level of -9 dBr. Fig. 2–5 shows the AVC output level versus its input level. For volume and baseband registers set to 0 dB, a level of 0 dBr corresponds to full scale input/output.

Fig. 2-5: Simplified AVC characteristics

## 2.4.2.4. Balance and Volume

To minimize quantization noise, the main volume control is automatically split into a digital and an analog part. The volume range is -114...+12 dB with an additional mute position. A balance function is provided.

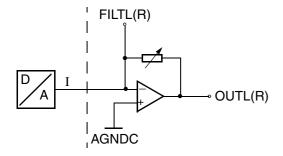

#### 2.4.3. D/A Converters

One pair of Micronas' unique multibit sigma-delta D/A converters is used to convert the audio data with high linearity and a superior S/N. In order to attenuate high-frequency noise caused by noise-shaping, internal low-pass filters are included. They require additional external capacitors between pins FILTx and OUTx (see Section 5.1. on page 87).

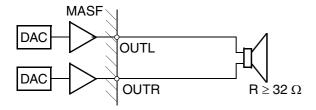

## 2.4.4. Output Amplifiers

The integrated output amplifiers are capable of directly driving stereo headphones or loudspeakers of 16 to 32  $\Omega$  impedance via 22  $\Omega$  series resistors. If more output power is required, the right output signal can be inverted and a single loudspeaker can be connected as a bridge between pins OUTL and OUTR. In this case, the source should be set to mono for optimized power.

Fig. 2-6: Bridge operation mode

#### 2.5. Clock Management

The MAS 35x9F is driven by a single crystal-controlled clock with a frequency of 18.432 MHz. It is possible to drive the MAS 35x9F with other reference clocks. In this case, the nominal crystal frequency must be written into memory location D0:348. The crystal clock acts as a reference for the embedded synthesizer that generates the internal clock.

For compressed audio data reception, the MAS 35x9F may act either as the clock master (Demand Mode) or as a slave (Broadcast Mode) as defined by bit[1] in IOControlMain memory cell (see Table 3–9 on page 33). In both modes, the output of the clock synthesizer depends on the sample rate of the decoded data stream as shown in Table 2–1.

In the BROADCAST MODE (PLL on), the incoming audio data controls the clock synthesizer via a PLL.

In the DEMAND MODE (PLL off) the MAS 35x9F acts as the system master clock. The data transfer is triggered by a demand signal at pin  $\overline{\text{EOD}}$ .

#### 2.5.1. DSP Clock

The DSP clock has a separate divider. In order to reduce the power consumption, it is set to the lowest acceptable rate of the synthesizer clock which is capable to allow the processor core to perform all tasks.

## 2.5.2. Clock Output At CLKO

If the DSP or audio codec functions are enabled (bits[11] or [10] in the Control Register at  $I^2C$  subaddress  $6A_{hex}$ ), the reference clock at pin CLKO is derived from the synthesizer clock.

Dependent on the sample rate of the decoded signal a scaler is applied which automatically divides the clock-out by 1, 2, or 4, as shown in Table 2–1. An additional division by 2 may be selected by setting bit[17] of the OutClkConfig memory cell (see Table 3–9 on page 33). The scaler can be disabled by setting bit[8] of this cell.

The controlling at OutClkConfig is only possible as long as the DSP is operational (bit[10] of the Control Register). Settings remain valid if the DSP is disabled by clearing bit[10].

**Table 2–1:** Settings of bits[8] and [17] in OutClkConfig and resulting CLKO output frequencies

|                     | Output Frequency at CLKO/MHz |                    |                    |                                                     |         |  |  |  |

|---------------------|------------------------------|--------------------|--------------------|-----------------------------------------------------|---------|--|--|--|

| f <sub>s</sub> /kHz | Synth.<br>Clock<br>bit[8]=1  |                    | er On<br>bit[17]=0 | Scaler Plus<br>Extra Division<br>bit[8]=0, bit[17]= |         |  |  |  |

| 48                  | 24.576                       | 512⋅f <sub>s</sub> | 24.576             | 256·f <sub>s</sub>                                  | 12.288  |  |  |  |

| 44.1                | 22.5792                      | O12 is             | 22.5792            | 200 is                                              | 11.2896 |  |  |  |

| 32                  | 24.576                       | 768·f <sub>s</sub> | 24.576             | 384·f <sub>s</sub>                                  | 12.288  |  |  |  |

| 24                  | 24.070                       | 512⋅f <sub>s</sub> | 12.288             | 256·f <sub>s</sub>                                  | 6.144   |  |  |  |

| 22.05               | 22.5792                      | O12 is             | 11.2896            | 200 is                                              | 5.6448  |  |  |  |

| 16                  | 24.576                       | 768·f <sub>s</sub> | 12.288             | 384·f <sub>s</sub>                                  | 6.144   |  |  |  |

| 12                  | 21.070                       | 512·f <sub>s</sub> | 6.144              | 256·f <sub>s</sub>                                  | 3.072   |  |  |  |

| 11.025              | 22.5792                      | O I L IS           | 5.6448             | 200 is                                              | 2.8224  |  |  |  |

| 8                   | 24.576                       | 768·f <sub>s</sub> | 6.144              | 384·f <sub>s</sub>                                  | 3.072   |  |  |  |

#### 2.6. Power Supply Concept

The MAS 35x9F was designed for minimal power dissipation. In order to optimize the battery management in portable players, two DC/DC converters were implemented to supply the complete portable audio player with regulated voltages.

#### 2.6.1. Power Supply Regions

The MAS 35x9F has five power supply regions.

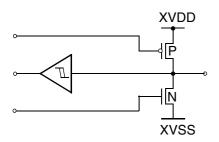

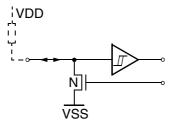

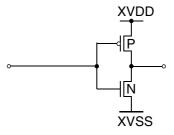

The VDD/VSS pin pair supplies all digital parts including the DSP core, the XVDD/XVSS pin pair is connected to the digital signal pin output buffers, the AVDD0/AVSS0 supply is for the analog output amplifiers, AVDD1/AVSS1 for all other analog circuits like clock oscillator, PLL circuits, system clock synthesizer and A/D and D/A converters. The I<sup>2</sup>C interface has an own supply region via pin I2CVDD. Connecting this to the microcontroller supply assures that the I<sup>2</sup>C bus always works as long as the microcontroller is alive so that the operating modes can be selected.

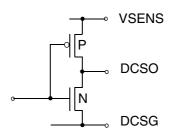

Beside these regions, the DC/DC converters have start-up circuits of their own which get their power via pin VSENSx.

#### 2.6.2. DC/DC Converters

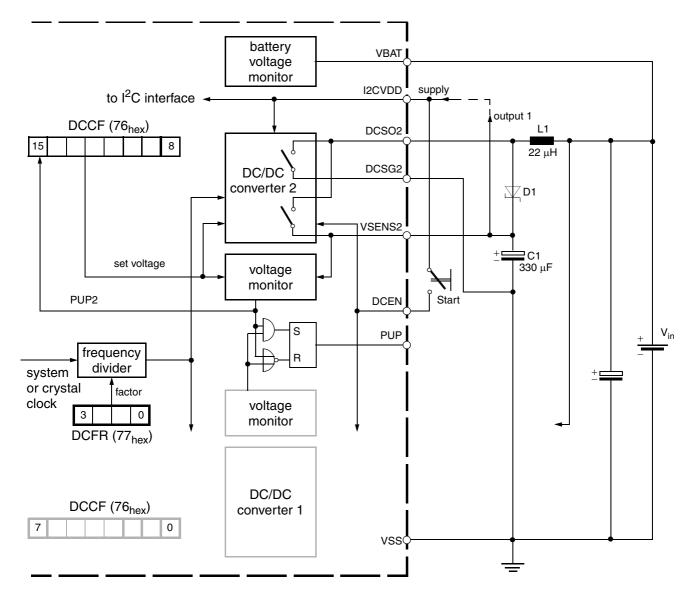

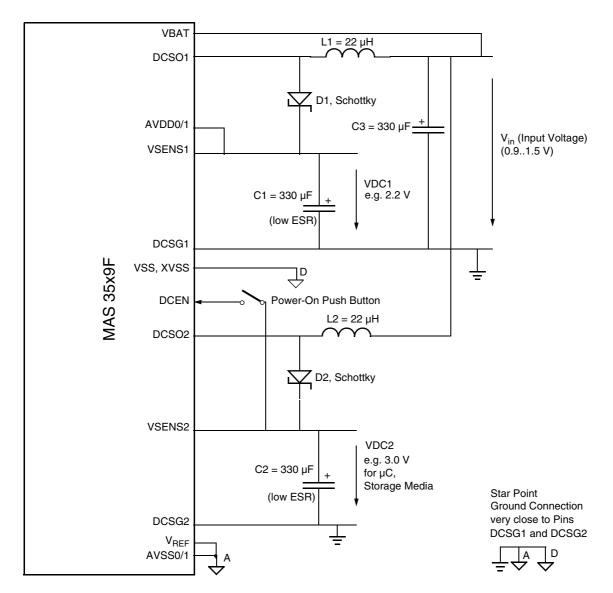

The MAS 35x9F has two embedded high-performance step-up DC/DC converters with synchronous rectifiers to supply both the DSP core itself and external circuitry such as a controller or flash memory at two different voltage levels. An overview is given in Fig. 2–7 on page 13.

The DC/DC converters are designed to generate an output voltage between 2.0 V and 3.5 V which can be programmed separately for each converter via the  $I^2C$  interface (see table 3.3). Both converters are of bootstrapped type allowing to start up from a voltage down to 0.9 V for use with a single battery or NiCd/NiMH cell. The default output voltages are 3.0 V. Both converters are enabled with a high level at pin DCEN and enabled/disabled by the  $I^2C$  interface.

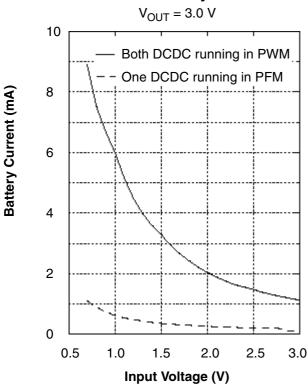

The MAS 35x9F DC/DC converters feature a constant-frequency, low noise pulse width modulation (PWM) mode and a low quiescent current, pulse frequency modulation (PFM) mode for improved efficiencies at low current loads. Both modes – PWM or PFM – can be selected independently for each converter via I<sup>2</sup>C interface. The default mode is PWM.

In PWM mode the switching frequency of the power-MOSFET-switches is derived from the crystal oscillator. Switching harmonics generated by constant frequency operation are consistent and predictable.

When the audio codec is enabled, the switching frequency of the converters is synchronised to the audio codec clock to avoid interferences into the audio band. The actual switching frequency can be selected via the I<sup>2</sup>C-interface between 300 kHz and 580 kHz (for details see DCFR Register in Table 3–4 on page 25).

In the PFM operation mode, the switching frequency is controlled by the converters themselves. It will be just high enough to service the output load, thus resulting in the best possible efficiency at low current loads. The PFM mode does not need a clock signal from the crystal oscillator. If both converters do not use the PWM-mode, the crystal clock will be shut down as long it is not needed by other internal blocks.

The synchronous rectifier bypasses the external Schottky diode to reduce losses caused by the diode forward voltage providing up to 5% efficiency improvement. By default, the P-channel synchronous rectifier switch is turned on when the voltage at pin(s) DCSOn exceeds the converter's output voltage at pin(s) VSENSn, and is turned off when the inductor current drops below a threshold. If one or both converters are disabled, the corresponding P-channel switch will be turned on, connecting the battery voltage to the DC/DC converters output voltage at pin VSENSn. However, it is possible to individually disable both synchronous rectifier switches by setting the corresponding bits (bit[8] and [0] in DCCF-register).

If both DC/DC-converters are off, a high signal may be applied at pin DCEN. This will start the converters in their default mode (PWM with 3.0 V output voltage). The PUP signal will change from low to high when both converters have reached their nominal output voltage and will return to low when both converters output voltages have dropped 200 mV below their programmed output voltage. The signal at pin PUP can be used to control the reset of an external microcontroller (see Section 2.11.2. on page 18 for details on the start-up procedure).

If only DC/DC-converter 1 is used, the output of the unused converter 2 (VSENS2) must be connected to the output of converter 1 (VSENS1) to make the PUP signal work properly. Also, if a DC/DC-converter is not used (no inductor connected), the pin DCSO must be left vacant.

#### 2.6.3. Power Supply Configurations

One of the following supply configurations may be used:

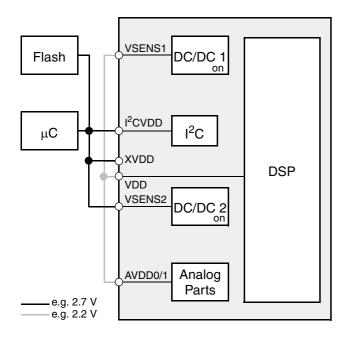

- Power-optimized solution (recommended operation). DC/DC 1 (e.g. 2.2 V) drives the MAS 35x9F DSP and the audio circuitry, DC/DC 2 (e.g. 2.7 V) supplies controller and flash (see Fig. 2–8 on page 14)

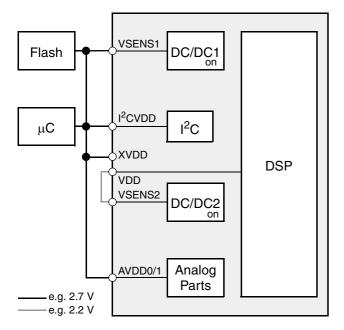

- Volume-optimized solution. DC/DC 1 (e.g. 2.7 V) supplies controller, flash and MAS 35x9F audio parts, DC/DC 2 generates e.g. 2.2 V for the MAS 35x9F DSP (see Fig. 2–9 on page 14).

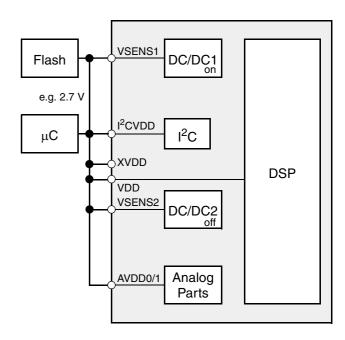

- Minimized external components. DC/DC 1 operates on, e.g., 2.7 V and feeds all components, DC/DC 2 remains off (see Fig. 2–10 on page 14).

- External power supply. All components are powered by an external source, no DC/DC converter is used (see Fig. 2–11 on page 14).

If DC/DC converter 1 is used, it must supply the analog circuits (pins AVDD0, AVDD1) of the MAS 35x9F.

If only one DC/DC converter is required, DC/DC1 must be used. Pin DCSO2 must be left vacant, pin VSENS2 should be connected to pin VSENS1.

If the DC/DC converters are not used, pin DCEN must be connected to VSS, DCSOx must be left vacant.

Fig. 2–7: DC/DC converter overview. The DCEN input must be connected to pin I2CVDD via start-up push button.

Fig. 2-8: Solution 1: Power-optimized

Fig. 2-10: Solution 3: Minimized components

Fig. 2-9: Solution 2: Volume-optimized

Fig. 2-11: Solution 4: External power supply

#### 2.7. MP3 Block Input Mode

A new so-called **MP3 block input** mode is now available which improves the input timing behavior of the MAS 35x9F MPEG 1/2/2.5 Layer 3 decoder. The following sections provide a detailed description of this new mode.

# 2.7.1. Functional Description of the MP3 Block Input Mode

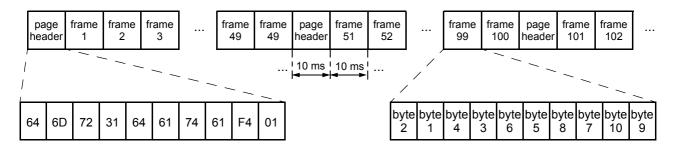

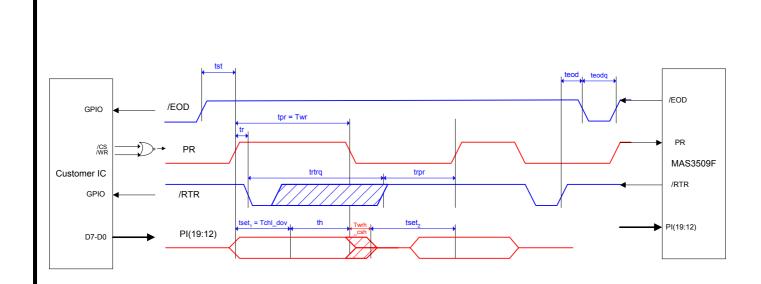

In MP3 block input, the MAS 35x9F generates a demand for new input data each time one of its two input buffers becomes available. The controller then has to send one block of input data via the serial interface SDIB. The block size is 2048 byte. The demand is signalized via a pulse on the  $\overline{\text{EOD}}$  pin.

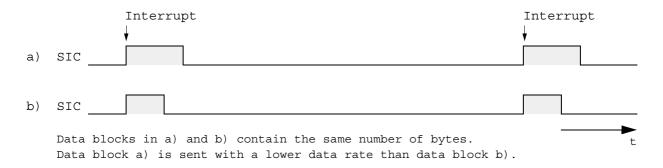

Fig. 2–12 shows that the number of interrupts per second does not depend on the data rate at the serial interface. The maximum input data bit clock rate supported by the MAS 35x9F for all MPEG audio sampling rates is 1.4 MHz.

Table 2–2 shows the average number of interrupts per second for several typical MP3 bit rates.

The time period between two interrupts may vary slightly even for fixed bit rate input streams due to the MP3 specific bit reservoir.

Table 2–2: MP3 bit rate vs. number of interrupts

| Bit Rate<br>[kbit/s] | Number of Interrupts [1/s] |

|----------------------|----------------------------|

| 320                  | 20                         |

| 256                  | 16                         |

| 224                  | 14                         |

| 192                  | 12                         |

| 160                  | 10                         |

| 128                  | 8                          |

| 112                  | 7                          |

| 96                   | 6                          |

| 80                   | 5                          |

| 64                   | 4                          |

Fig. 2-12: Data Block Timing Diagram

#### 2.7.2. Setup

Table 3–3 on page 24 lists the new bits, UIC cells, and registers to setup the MP3 block input mode.

#### 2.7.2.1. Resync Timeout

In case the MP3 decoder loses the synchronization (e.g. due to corrupted input data), the output is softly muted and a resync loop is entered where the MAS 35x9F can be accessed via I<sup>2</sup>C. The loop is left and the re-synchronization procedure continues in any of the following cases:

- the last input data block is fully sent,

- the Validate bit of IOControlMain is set (D0:346, bit[0]),

- the timeout is reached (ResyncTimeout in Table 3–3), the end bit is set (this bit will be reset by the MAS 35x9F).

## 2.7.2.2. Detailed Setup

After the MPEG audio decoder application has been selected, the following settings enable the MP3 block decoding process.

#### Play MP3

- 1. Write 0x318 into SerialInConfig.

- 2. Write IOControlMain with bit[2] and bit[0] equal one.

- 3. Write IOControlMain with bit[2] equals zero and bit[0] equals one.

- 4. Write 0x0 into ResyncTimeout.

- 5. Write 0x0 into SoftMute.

- 6. Enable EODQ interrupt for sending data in controller.

- 7. Set StartBit in MP3BlockConfig.

- Send data block of 2048 byte when EODQ goes high.

### Stop/Pause MP3

- 1. Write 0x1 into SoftMute.

- 2. Clear start bit in MP3BlockConfig.

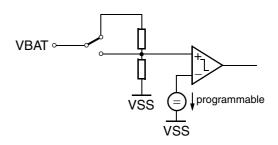

## 2.8. Battery Voltage Supervision

Independent of the DC/DC converters, a battery voltage supervision circuit (at pin VBAT) is provided. It can be programmed to supervise one or two battery cells. The voltage is measured by subsequently setting a series of voltage thresholds and checking the respective comparison result in register  $77_{\rm hex}$ .

#### 2.9. Interfaces

The MAS 35x9F uses an I<sup>2</sup>C control interface, a serial input interface for MPEG bit streams, and digital audio output interfaces for the decoded audio data (I<sup>2</sup>S and S/PDIF). S/PDIF input is available after Software download. A parallel I/O interface (PIO) may be used for fast data exchange.

# 2.9.1. I<sup>2</sup>C Control Interface

For controlling and program download purposes, a standard I<sup>2</sup>C slave interface is implemented. A detailed description of all functions can be found in Section 3.

## 2.9.2. S/PDIF Input Interface

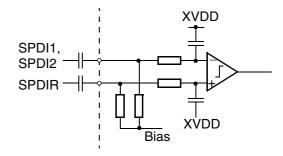

The S/PDIF interface receives a one-wire serial bus signal. In addition to the signal input pin SPDI1/SPDI2, a reference pin SPDIR is provided to support balanced signal sources or twisted pair transmission lines.

The synchronization time on the input signal is < 50 ms.

S/PDIF input is not supported for MPEG 1/2 Layer 2/3 and MPEG 2 AAC.

Micronas has developed a download software for flexible usage of the S/PDIF I/O and SDI/SDO interfaces. It is described in Download Software Supplement I2SPDIF (6251-505-1PDS).

#### 2.9.3. S/PDIF Output

The S/PDIF output of the baseband audio signals is implemented at pin SPDO since version B4.

The channel status bits can be set as described in Table 3–9.

## 2.9.4. Multiline Serial Audio Input (SDI, SDIB)

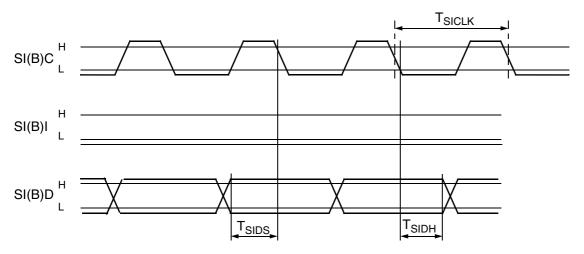

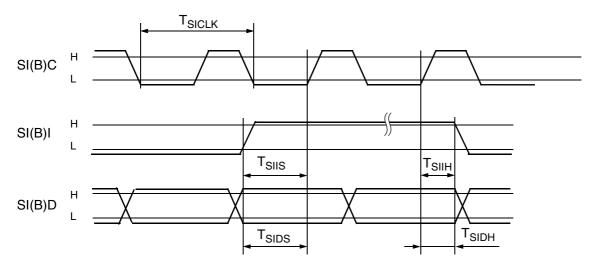

There are two multiline serial audio input interfaces (SDI, SDIB) each consisting of the three pins SI(B)C, SI(B)I, and SI(B)D. The standard firmware only supports SDIB for bit-stream signals, while PCM-inputs should be routed to SDI.

The interfaces can be configured as continuous bitstream or word-oriented inputs. For the MPEG bit streams, the word strobe pin SIBI must always be connected to  $V_{SS}$ ; bits must be sent MSB first as created by the encoder.

If the download software (refer to Download Software Supplement I2SPDIF (6251-505-1PDS)) is used, the interface acts as an I<sup>2</sup>S-type with SI(B)I as a word-strobe for PCM data.

For the Demand Mode (see Section 2.5.), the signal clock coming from the data source must be higher than the nominal data transmission rate (e.g. 128 kbit/s). Pin EOD is used to interrupt the data flow whenever the input buffer of the MAS 35x9F is filled.

For controlling details, please refer to Table 3–9 on page 33.

#### 2.9.5. Multiline Serial Output (SDO)

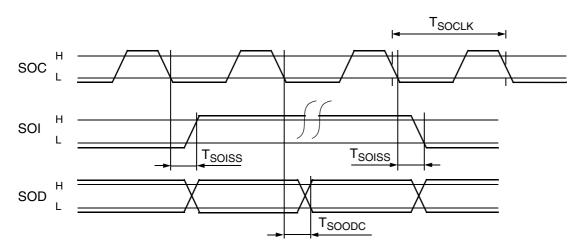

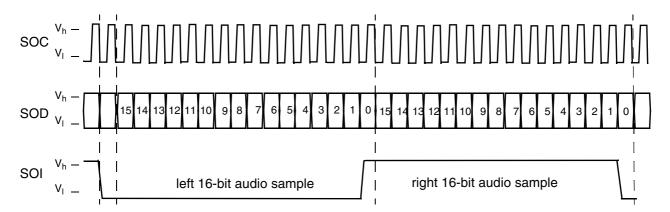

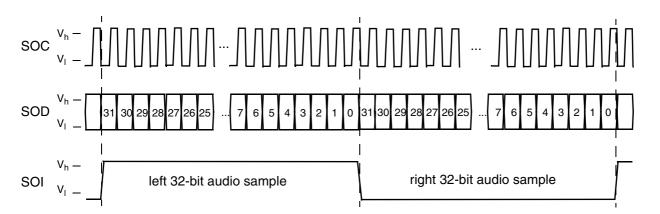

The serial audio output interface of the MAS 35x9F is a standard  $I^2S$ -like interface consisting of the data lines SOD, the word strobe SOI and the clock signal SOC. It is possible to choose between two standard interface configurations (16-bit data words with word strobe time offset or 32-bit data words with inverted SOI signal).

If the serial output generates 32 bits per audio sample, only the first 20 bits will carry valid audio data. The 12 trailing bits are set to zero by default.

#### 2.9.6. Parallel Input/Output Interface (PIO)

The parallel interface of the MAS 35x9F consists of the 8 data lines PI12...PI19 (MSB) and the control lines PCS, PR, PRTR, PRTW, and EOD. It can be used for data exchange with an external memory, for fast program download and for other special purposes as defined by the DSP software.

For MPEG data input, the PIO interface is activated by setting bits[9] and [8] in D0:346 to 01. For the handshake protocol, please refer to Section 4.6.2.8. on page 78.

#### 2.10. MPEG Synchronization Output

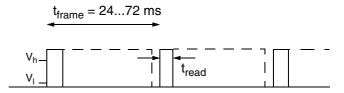

The signal at pin SYNC is set to '1' after the internal decoding for the MPEG header has been finished for one frame. The rising edge of this signal can be used as an interrupt input for the controller that triggers the read out of the control information and ancillary data. As soon as the MAS 35x9F has received the SYNC reset command (see Section 4.6.2.6. on page 75), the SYNC signal is cleared. If the controller does not issue a reset command, the SYNC signal returns to '0' as soon as the decoding of the next MPEG frame is started. MPEG status and ancillary data become invalid until the frame is completely decoded and the signal at pin SYNC rises again. The controller must have finished reading all MPEG information before it becomes invalid. The MPEG Layer 2/3 frame lengths are given in Table 2-3. AAC has no fixed frame length.

**Fig. 2–13:** Schematic timing of the signal at pin SYNC. The signal is cleared at t<sub>read</sub> when the controller has issued a Clear SYNC Signal command (see Section 4.6.2.6. on page 75). If no command is issued, the signal returns to '0' just before the decoding of the next MPEG frame.

Table 2-3: Frame length in MPEG Layer 2/3

| f <sub>s</sub> /kHz | Frame Length<br>Layer 2 | Frame Length<br>Layer 3 |

|---------------------|-------------------------|-------------------------|

| 48                  | 24 ms                   | 24 ms                   |

| 44.1                | 26.12 ms                | 26.12 ms                |

| 32                  | 36 ms                   | 36 ms                   |

| 24                  | 24 ms                   | 24 ms                   |

| 22.05               | 26.12 ms                | 26.12 ms                |

| 16                  | 36 ms                   | 36 ms                   |

| 12                  | not available           | 48 ms                   |

| 11.025              | not available           | 52.24 ms                |

| 8                   | not available           | 72 ms                   |

#### 2.11.Default Operation

This sections refers to the standard operation mode "power-optimized solution" (see Section 2.6.3.).

#### 2.11.1. Stand-by Functions

After applying the battery voltage, the system will remain stand-by, as long as the DCEN pin level is kept low. Due to the low stand-by current of CMOS circuits, the battery may remain connected to DCSOn/VSENSn at all times.

# 2.11.2. Power-Up of the DC/DC Converters and Reset

The battery voltage must be applied to pin DCSOn via the 22  $\mu$ H inductor and, furthermore, to the sense pin VSENSn via a Schottky diode (see Fig. 2–7 on page 13).

For start-up, the pin DCEN must be connected via an external "start" push button to the I2CVDD supply, which is equivalent to the battery supply voltage (> 0.9 V) at start-up.

The supply at DCEN must be applied until the DC/DC converters have started up (signal at pin PUP) and then removed for normal operation.

As soon as the output voltage at VSENSn reaches the default voltage monitor reset level of 3.0 V, the respective internal PUPn bit will be set. When both PUPn bits are set, the signal at pin PUP will go high and can be used to start and reset the microcontroller.

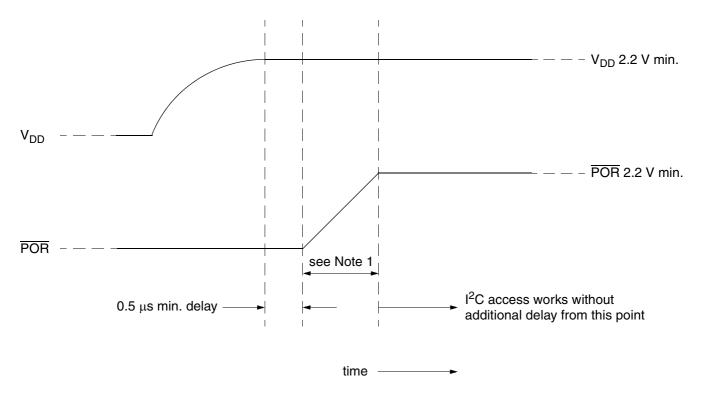

Before transmitting any  $I^2C$  commands, the controller must issue a power-on reset to pin  $\overline{POR}$ . The separate supply pin I2CVDD ensures that the  $I^2C$  interface works independently from the DSP or the audio codec. Now the desired supply voltage can be programmed at  $I^2C$  subaddress  $76_{hex}$ .

## 2.11.2.1. Important Advice for Turn-on and Operating Voltage

Before the 2.2 V are programmed at the DCDC converter, DSP+Codec must be enabled.

Operating and Turn-Off is possible down to 2.2 V.

The sequence should be similar to the following:

- 1. Start DCDC

- 2. Set DCDC to 2.5 V

Turn on DSP+Codec

Write App-Select memory cell

Read App-Running Mem cell

If okay: Set DCDC to 2.2 V

Set other mem cells

Set other codec registers

- 3. Demute...send data

- 4. Mute...stop data.....loop "3)" "4)"...

- 5. Turn off DSP+Codec goto "2)" etc.....

The signal at pin PUP will return to low only when both PUPn flags (I $^2$ C subaddress  $76_{hex}$ ) have returned to zero. Care must be taken when changing both DC/DC output voltages to higher values. In this case, both output voltages are momentarily insufficient to keep the PUPn flags up; the resulting dip in the signal at the PUP pin may, in turn, reset the microcontroller. To avoid this condition, only one DC/DC output voltage should be changed at a time. Before modifying the second voltage, the microcontroller must wait for the PUPn flag of the first voltage to be set again.

If only DC/DC converter 1 is used, the reference voltage of the second, unused converter should be set to a lower value than that of converter 1, and its pin VSENS2 should be connected to VDD.

The operating mode pulse width modulation, or pulse frequency modulation, are controlled at  $I^2C$  subaddress  $76_{\text{hex}}$ , the operating frequency at  $I^2C$  subaddress  $77_{\text{hex}}$ .

# 2.11.3. Reset Signal Specification

After power-up, a reset signal should be applied to the pin  $\overline{POR}$  by the microcontroller as follows:

Fig. 2-14: Reset signal at pin POR

**Note:** The slew rate of  $\overline{\mathsf{POR}}$  should be as high as possible, but **must be glitch-free in any case**.

Slew rate typ.: 1  $\mu s$  for 10% to 90% level transition, Slew rate max.: 20  $\mu s$  for 10% to 90% level transition.

#### 2.11.4.Control of the Signal Processing

Before starting the DSP, the controller should check for a sufficient voltage supply (respective flag PUPn at  $I^2C$  subaddress  $76_{hex}$ ). The DSP is enabled by setting the appropriate bit in the Control register ( $I^2C$  subaddress  $6A_{hex}$ ). The nominal frequency of the crystal oscillator must be written into D0:348. After an initialization phase of 5 ms, the DSP data registers can be accessed via  $I^2C$ .

Input and output control is performed via memory location D0:346 and D0:347. The serial input interface SDIB is the default. The decoded audio can be routed to either the S/PDIF, the SDO and the analog outputs. The output clock signal at pin CLKO is defined in D0:349.

All changes in the D0 memory cells become effective synchronously upon setting the LSB of Main I/O Control (see Table 3–9 on page 33). Therefore, this cell should always be written last.

The digital volume control (see Table 3–9 on page 33) is applied to the output signal of the DSP. The decoded audio data will be available at the SPDO output interface in the next version.

The DSP does not have to be started if its functions are not required, e.g., for routing audio through the codec part of the IC via the A/D and the D/A converters.

#### 2.11.5.Start-up of the Audio Codec

Before enabling the audio codec, the controller should check for a sufficient voltage supply (respective flag PUPn at I<sup>2</sup>C subaddress 76<sub>hex</sub>).

The audio codec is enabled by setting the appropriate bit at the Control register (I $^2$ C subaddress 6A $_{\rm hex}$ ). After an initialization phase of 5 ms, the DSP data registers can be accessed via I $^2$ C. The A/D and the D/A converters must be switched on explicitly (register 00 00 $_{\rm hex}$  at I $^2$ C subaddress 6C $_{\rm hex}$ ). The D/A converters may either accept data from the A/D converters or the output of the DSP, or a mix of both  $^{1)}$  (register 00 06 $_{\rm hex}$  and 00 07 $_{\rm hex}$  at I $^2$ C subaddress 6C $_{\rm hex}$ ). Finally, an appropriate output volume (register 00 10 $_{\rm hex}$  at I $^2$ C subaddress 6C $_{\rm hex}$ ) must be selected.

#### 2.11.6.Power-Down

All analog outputs should be muted and the A/D and the D/A converters must be switched off (register 00  $10_{hex}$  and 00  $00_{hex}$  at I<sup>2</sup>C subaddress  $6C_{hex}$ ). The DSP and the audio codec must be disabled (clear DSP\_EN and CODEC\_EN bits in the Control register, I<sup>2</sup>C subaddress  $6A_{hex}$ ). By clearing both DC/DC enable flags in the Control register (I<sup>2</sup>C subaddress  $6A_{hex}$ ), the microcontroller can power down the complete system.

<sup>1)</sup> mixer available in version A2 and later; in version A1, please use selector 00 0F<sub>hex</sub>.

## 3. Controlling

## 3.1. I<sup>2</sup>C Interface

Controlling between the MAS 35x9F and the external controller is done via an I<sup>2</sup>C slave interface.

#### 3.1.1. Device Address

The device addresses are  $3C/3E_{hex}$  (device write "DW") and  $3D/3F_{hex}$  (device read, "DR") as shown in Table 3–1. The device address pair  $3C/3D_{hex}$  applies if the DVS pin is connected to VSS, the device address pair  $3E/3F_{hex}$  applies if the DVS pin is connected to I2CVDD.

Table 3-1: I<sup>2</sup>C device address

| <b>A</b> 7 | <b>A6</b> | <b>A</b> 5 | <b>A</b> 4 | А3 | A2 | <b>A</b> 1 | W/R |

|------------|-----------|------------|------------|----|----|------------|-----|

| 0          | 0         | 1          | 1          | 1  | 1  | DVS        | 0/1 |

I<sup>2</sup>C clock synchronization is used to slow down the interface if required.

## 3.1.2. I<sup>2</sup>C Registers and Subaddresses

The interface uses one level of subaddresses. The MAS 35x9F interface has 7 subaddresses allocated for the corresponding  $I^2C$  registers. The registers can be divided into three categories as shown in Table 3–2.

The address  $6A_{\text{hex}}$  is used for basic control, i.e. reset and task select. The other addresses are used for data transfer from/to the MAS 35x9F.

The  $I^2C$  registers of the MAS 35x9F are 16 bits wide, the MSB is denoted as bit[15]. Transmissions via  $I^2C$  bus have to take place in 16-bit words (two byte transfers, MSB sent first); thus, for each register access, two 8-bit data words must be sent/received via  $I^2C$  bus.

## 3.1.3. Naming Convention

The description of the various controller commands uses the following formalism:

- Abbreviations used in the following descriptions:

- a address

- d data value

- n count value

- o offset value

- r register number

- x don't care

- Memory addresses, like D1:89f, are always in hexadecimal notation.

- A data value is split into 4-bit nibbles which are numbered beginning with 0 for the least significant

nibble.

- Data values in nibbles are always shown in hexadecimal notation.

- A hexadecimal 20-bit number **d** is written, e.g. as  $\mathbf{d} = 17C63_{hex}$ , its five nibbles are  $d0 = 3_{hex}$ ,  $d1 = 6_{hex}$ ,  $d2 = C_{hex}$ ,  $d3 = 7_{hex}$ , and  $d4 = 1_{hex}$ .

- Variables used in the following descriptions:

PC address:

DW3C/3E<sub>hex</sub> PC device write

DR3D/3F<sub>hex</sub> PC device read

DSP core:

data\_write68<sub>hex</sub>DSP data write data\_read69<sub>hex</sub>DSP data read Codec:

codec\_write6C<sub>hex</sub>codec write codec\_read6D<sub>hex</sub>codec read

- Bus signals

S Start P Stop

A ACK = Acknowledge

N NAK = Not acknowledge

W Wait =  $I^2C$  clock line is held low

while the MAS 35x9F is processing the current I<sup>2</sup>C command

- Symbols in the telegram examples

< Start Condition

> Stop

dd data bytes

xx ignore

All telegram numbers are hexadecimal, data originating from the MAS 35x9F are represented as gray letters.

Example:

<DW 68 dd dd > write data to DSP <DW 69 <DR dd dd > read data from DSP

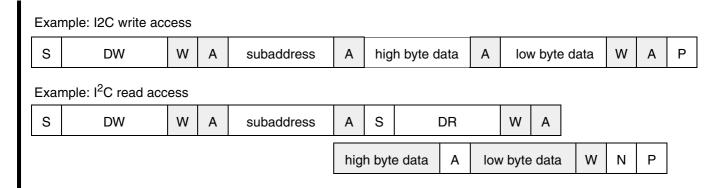

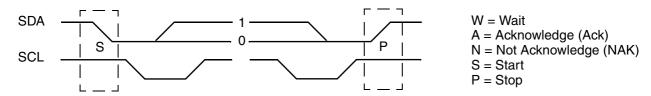

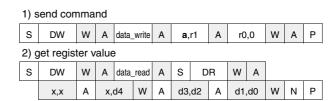

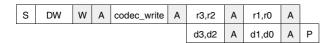

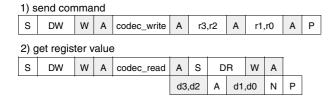

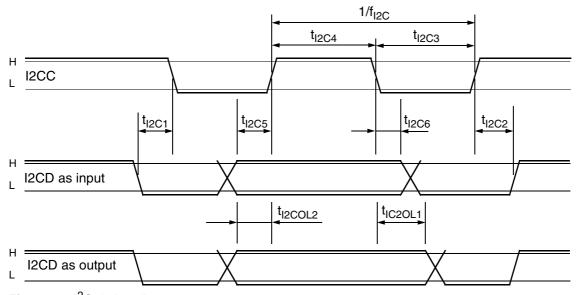

Fig. 3–1 shows I<sup>2</sup>C bus protocols for write and read operations of the interface; the read operations require an extra start condition and repetition of the chip address with the device read command (DR). Fields with signals/data originating from the MAS 35x9F are marked by a gray background.

**Note:** In some cases the data reading process must be concluded by a NAK condition.

### 3.2. Direct Configuration Registers

The task selection of the DSP and the DC/DC converters are controlled in the direct configuration registers CONTROL, DCCF, and DCFR.

Table 3-2: I<sup>2</sup>C subaddresses

| Sub-<br>address<br>(hex) | I <sup>2</sup> C-<br>Register<br>Name | Function                                                 |  |  |  |  |  |  |  |

|--------------------------|---------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|

| Direct Configuration     |                                       |                                                          |  |  |  |  |  |  |  |

| 6A                       | CONTROL                               | Controller writes to<br>MAS 35x9F CONTROL<br>register    |  |  |  |  |  |  |  |

| 76                       | DCCF                                  | Controller writes to first DC/DC configuration register  |  |  |  |  |  |  |  |

| 77                       | DCFR                                  | Controller writes to second DC/DC configuration register |  |  |  |  |  |  |  |

| DSP Core                 | e Access                              |                                                          |  |  |  |  |  |  |  |

| 68                       | data_write                            | Controller writes to<br>MAS 35x9F DSP                    |  |  |  |  |  |  |  |

| 69                       | data_read                             | Controller reads from<br>MAS 35x9F DSP                   |  |  |  |  |  |  |  |

| Codec A                  | ccess                                 |                                                          |  |  |  |  |  |  |  |

| 6C                       | codec_write                           | Controller writes to<br>MAS 35x9F codec regis-<br>ter    |  |  |  |  |  |  |  |

| 6D                       | codec_read                            | Controller reads from<br>MAS 35x9F codec regis-<br>ter   |  |  |  |  |  |  |  |

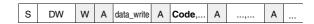

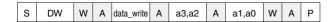

## 3.2.1. Write Direct Configuration Registers

| s | DW | W | Α | subaddr. | Α | d3,d2 | Α | d1,d0 | Α | Р |

|---|----|---|---|----------|---|-------|---|-------|---|---|

|   |    |   |   |          |   |       |   |       |   |   |

The write protocol for the direct configuration registers only consists of device address, subaddress and one 16-bit data word.

# 3.2.2. Read Direct Configuration Register

| S | DW | W | Α | subaddr. | Α | S   | D  | R | W  | Α   |   |   |

|---|----|---|---|----------|---|-----|----|---|----|-----|---|---|

|   |    |   |   |          |   | d3, | d2 | Α | d1 | ,d0 | Ν | Р |

To check the PUP1 and PUP2 power-up flags, it is necessary to read back the content of the direct configuration registers.

Fig. 3–1: Example of an I<sup>2</sup>C bus protocol for the MAS 35x9F (MSB first; data must be stable while clock is high)

Table 3–3: L3 block input mode user interface (all addresses in hex notation)

| Addr.  | Name              | Description                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0:346 | IOControlMain     | bit[15] MP3 block input select 0: MP3 block input mode OFF 1: MP3 block input mode ON works for input at serial input interface B (bit[9:8] of IOControlMain = 00 <sub>bin</sub> )                                                                                           |  |  |  |  |  |

|        |                   | Reset value is 0x8024 (see Table 3–2).                                                                                                                                                                                                                                       |  |  |  |  |  |

| R0:68  | MP3BlockConfig    | bit[17] data end bit Disables resync timeout. Should be set by the controller at the end of an input file (file end, stop, or pause) when the last requested data block has been fully sent.  0: resync timeout enabled 1: resync timeout disable ↔ no wait for end of block |  |  |  |  |  |

|        |                   | bit[16] reserved, set to "0"                                                                                                                                                                                                                                                 |  |  |  |  |  |

|        |                   | bit[15] start data request 0: MP3 decoder does not send data requests (wait loop) 1: MP3 decoder in operational mode, new input data will be requested via pulses at the demand pin.                                                                                         |  |  |  |  |  |

|        |                   | bit[14:0] input block size specific value, do not modify                                                                                                                                                                                                                     |  |  |  |  |  |

|        |                   | Reset value is 0x6670. To set the start bit, the controller must write 0xe670.                                                                                                                                                                                               |  |  |  |  |  |

| R0:7e  | PulseDelayCounter | bit[13:0] determines the variable fraction of the demand pulse length. pulseLenVar[ns] = value * 88.58.                                                                                                                                                                      |  |  |  |  |  |

| D0:34e | ResyncTimeout     | bit[19:0] timeout after resync: timeout[ $\mu$ s] = value * 3.32. The default value is 2 <sup>19</sup> -1, which results in a timeout of 1.74 seconds. For an optimized resync behavior, it is recommended to set this value to zero.                                        |  |  |  |  |  |

| R0:5b  | SerialInConfig    | bit[14:0] configuration of the serial input interface                                                                                                                                                                                                                        |  |  |  |  |  |

| D0:350 | SoftMute          | bit[0] MP3 soft mute 0: audio output on 1: audio output soft muted                                                                                                                                                                                                           |  |  |  |  |  |

Table 3-4: Direct configuration registers

| I <sup>2</sup> C Sub-<br>address<br>(hex) | Function                                                              |                                                                                                                                                                                                                                                                | Name    |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|--|

| 6A                                        | Control Re                                                            | egister (reset value = 3000 <sub>hex</sub> )                                                                                                                                                                                                                   | CONTROL |  |  |  |  |  |  |

|                                           | bit[15:14]                                                            | Analog supply voltage range                                                                                                                                                                                                                                    |         |  |  |  |  |  |  |

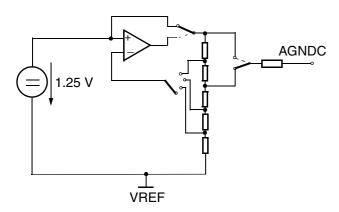

|                                           |                                                                       | Code         AGNDC         recommended for voltage range of AVDD           00         1.1 V         2.0 2.4 V (reset)           01         1.3 V         2.4 3.0 V           10         1.6 V         3.0 3.6 V           11         reserved         reserved |         |  |  |  |  |  |  |

|                                           | Higher volt noise ratio.                                              | tage ranges permit higher output levels and thus a better signal-to-                                                                                                                                                                                           |         |  |  |  |  |  |  |

|                                           | bit[13]<br>bit[12]                                                    |                                                                                                                                                                                                                                                                |         |  |  |  |  |  |  |

|                                           | Both DC/D                                                             | Both DC/DC converters are switched on by default with DCEN = high (1).                                                                                                                                                                                         |         |  |  |  |  |  |  |

|                                           | bit[11]<br>bit[10]                                                    | Enable and reset audio codec <sup>2)</sup> Enable and reset DSP core <sup>2)</sup>                                                                                                                                                                             |         |  |  |  |  |  |  |

|                                           | For normal<br>core and the<br>The DSP of<br>the analog<br>can be left |                                                                                                                                                                                                                                                                |         |  |  |  |  |  |  |

|                                           | bit[9]<br>bit[8]                                                      | Reset codec<br>Reset DSP core                                                                                                                                                                                                                                  |         |  |  |  |  |  |  |

|                                           | bit[7]                                                                |                                                                                                                                                                                                                                                                |         |  |  |  |  |  |  |

|                                           | bit[6:0]                                                              | Reserved, must be set to zero                                                                                                                                                                                                                                  |         |  |  |  |  |  |  |

<sup>1)</sup> refer to Section 4.6.3. on page 79 <sup>2)</sup> refer to Section 2.11.2.1.

25

Table 3-4: Direct configuration registers, continued

| I <sup>2</sup> C Sub-<br>address<br>(hex) | Function    |                                                                                                                                                                     |                                                                                                          |                                                                                                                                                    |                                                                                                                 | Name |  |  |  |  |

|-------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 76                                        | DCCF Reg    | <b>jister</b> (reset                                                                                                                                                | = 5050 <sub>hex</sub> )                                                                                  |                                                                                                                                                    |                                                                                                                 | DCCF |  |  |  |  |

|                                           | DC/DC Co    | nverter 2                                                                                                                                                           |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

|                                           | bit[15]     | PUP2: Vol                                                                                                                                                           | tage monitor 2                                                                                           | 2 flag (readb                                                                                                                                      | ack)                                                                                                            |      |  |  |  |  |

|                                           | bit[14:11]  | Converter                                                                                                                                                           | 2 output volta                                                                                           | ge with resp                                                                                                                                       | ect to VREF <sup>2)</sup>                                                                                       |      |  |  |  |  |

|                                           |             | Code  1111 1110 1101 1100 1011 1000 0111 0110 0101 0100 <sup>1)</sup> 0011 <sup>1)</sup> 0010 <sup>1)</sup>                                                         | Nominal output volt. 3.5 V 3.4 V 3.3 V 3.2 V 3.1 V 3.0 V 2.9 V 2.8 V 2.7 V 2.6 V 2.5 V 2.4 V 2.3 V 2.2 V | set level<br>of PUP2<br>3.4 V<br>3.3 V<br>3.2 V<br>3.1 V<br>3.0 V<br>2.9 V<br>2.8 V<br>2.7 V<br>2.6 V<br>2.5 V<br>2.4 V<br>2.3 V<br>2.2 V<br>2.1 V | reset level of PUP2 3.3 V 3.2 V 3.1 V 3.0 V 2.9 V 2.8 V (reset) 2.7 V 2.6 V 2.5 V 2.4 V 2.3 V 2.2 V 2.1 V 2.0 V |      |  |  |  |  |

|                                           | bit[10]     | Mode<br>1<br>0                                                                                                                                                      | pulse freque                                                                                             | ation (PFM)<br>(PWM) (reset)                                                                                                                       |                                                                                                                 |      |  |  |  |  |

|                                           | bit[9:8]    | bit[9:8] Reserved, must be set to zero                                                                                                                              |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

|                                           | higher than | e DC/DC converters are up-converters only. Thus, if the battery voltage is her than the selected nominal voltage, the output voltage will exceed the ninal voltage. |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

|                                           | DC/DC Co    | nverter 1                                                                                                                                                           |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

|                                           | bit[7]      | PUP1: Vol                                                                                                                                                           | tage monitor 1                                                                                           | l flag (readb                                                                                                                                      | ack)                                                                                                            |      |  |  |  |  |

|                                           | bit[6:3]    | Converter (see bits 1                                                                                                                                               | 1 output voltage 4 to 11) <sup>2)</sup>                                                                  | ge at VSEN                                                                                                                                         | S1 with respect to VREF                                                                                         |      |  |  |  |  |

|                                           | bit[2]      | Mode<br>1<br>0                                                                                                                                                      | pulse freque                                                                                             |                                                                                                                                                    | ation (PFM)<br>(PWM) (reset)                                                                                    |      |  |  |  |  |

|                                           | bit[1:0]    | Reserved,                                                                                                                                                           | must be set to                                                                                           | o zero                                                                                                                                             |                                                                                                                 |      |  |  |  |  |

|                                           | main refere | the reference<br>ence source<br>sed, its outpu                                                                                                                      |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

|                                           |             | nus, if the battery voltage is put voltage will exceed the                                                                                                          |                                                                                                          |                                                                                                                                                    |                                                                                                                 |      |  |  |  |  |

$<sup>^{1)}</sup>$  refer to Section 4.3.3. on page 59  $^{2)}$  refer to Section 2.11.2.1.

Table 3-4: Direct configuration registers, continued

| I <sup>2</sup> C Sub-<br>address<br>(hex) | Function                                                               |                                                                                 |                                                                                                           |                                                                                                                                                         |                                                                                                                                                                                    | Name |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|